TI /H/10006-1

# **LM1201 Video Amplifier System**

## **General Description**

The LM1201 is a wideband video amplifier system intended for high resolution monochrome or RGB monitor applications. In addition to the wideband video amplifier the LM1201 contains a gated differential input black level clamp comparator for brightness control and an attenuator circuit for contrast control. The LM1201 also contains a voltage reference for the video input. For medium resolution RGB color monitor applications also see the LM1203 Video Amplifier System data sheet.

#### **Features**

- Wideband video amplifier (200 MHz @ -3 dB)

- Attenuator circuit for contrast control (>40 dB range)

- Externally gated comparator for brightness control

- Provisions for external gain set and peaking of video amplifier

- Video input voltage reference

- Low impedance output driver

## **Typical Applications**

- CRT video amplifiers

- Video switches

- High frequency video preamplifiers

- Wideband gain controls

- PC monitors

- Workstations

- Facsimile machines

- Printers

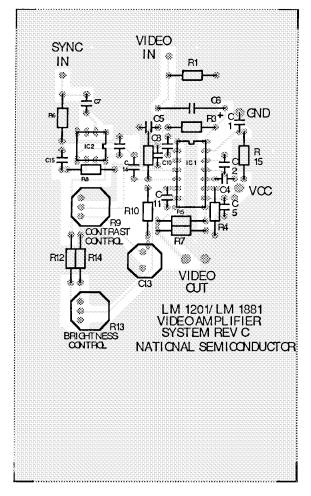

## **Block and Connection Diagram**

FIGURE 1

Order Number LM1201M or LM1201N See NS Package Number M16A or N16E

## **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage  $V_{CC}$  Pins 10, 12, 15

to Ground Pins, 1, 7  $\begin{tabular}{ll} 13.5V \\ Voltage at Any Input Pin (V_{IN}) & V_{CC} \ge V_{IN} \ge GND \\ Video Output Current (I_8) & 28 mA \\ Package Power Dissipation at T_A = 25 °C & 1.56W \\ \end{tabular}$

(Above 25°C derate based on ( $\theta_{JA}$  and  $T_{J}$ )

Package Thermal Resistance ( $\theta_{\rm JA}$ ) N16E 80°C/W Package Thermal Resistance ( $\theta_{\rm JA}$ ) M16A 100°C/W Junction Temperature (T<sub>J</sub>) 150°C

$Storage\ Temperature\ Range\ (T_{STG}) \qquad -65^{\circ}C\ to\ +150^{\circ}C$  Lead Temperature (Soldering, 10 sec.)  $265^{\circ}C$  ESD Susceptibility  $2\ kV$  Human body model: 100 pF discharged through a 1.5  $k\Omega$

## **Operating Ratings** (Note 4)

Temperature Range 0°C to +70°C Supply Voltage (V $_{CC}$ ) 10.8V  $\leq$  V $_{CC} \leq$  13.2V

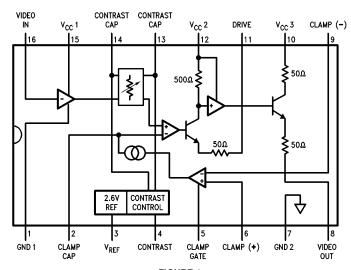

# $\textbf{Electrical Characteristics} \,\, \text{See Test Circuit (Figure 2), T}_{A} = 25^{\circ}\text{C; V}_{CC1} = \text{V}_{CC2} = \text{V}_{CC3} = 12\text{V}_{CC3} = 12\text$

DC Static Tests S9 Open; V4 = 6V; V5 = 0V; V6 = 2.0V unless otherwise stated

| Symbol                | Parameter                       | Conditions                               | Typical | Tested<br>Limit<br>(Note 1) | Design<br>Limit<br>(Note 2) | Units<br>(Limits) |

|-----------------------|---------------------------------|------------------------------------------|---------|-----------------------------|-----------------------------|-------------------|

| Is                    | Supply Current                  | V <sub>CC</sub> Pins 12, 15 Only         | 45      | 57                          |                             | mA(max)           |

| V <sub>3</sub>        | Video Input Reference Voltage   |                                          | 2.65    | 2.4                         |                             | V(min)            |

|                       |                                 |                                          |         | 2.95                        |                             | V(max)            |

| I <sub>16</sub>       | Video Input Bias Current        | (V <sub>3</sub> -V <sub>16</sub> )/10 kΩ | 5.0     | 20                          |                             | μA(max)           |

| V <sub>5L</sub>       | Clamp Gate Low Input Voltage    | Clamp Comparator On                      | 1.2     | 0.8                         |                             | V(min)            |

| V <sub>5H</sub>       | Clamp Gate High Input Voltage   | Clamp Comparator Off                     | 1.6     | 2.0                         |                             | V(max)            |

| I <sub>5L</sub>       | Clamp Gate Low Input Current    | V <sub>5</sub> = 0V                      | -0.5    | -5.0                        |                             | μA(max)           |

| I <sub>5H</sub>       | Clamp Gate High Input Current   | V <sub>5</sub> = 12V                     | 0.005   | 1                           |                             | μA(max)           |

| l <sub>2+</sub>       | Clamp Cap Charge Current        | V <sub>2</sub> = 0V                      | 1       | 0.55                        |                             | mA(min)           |

| -<br>I <sub>2</sub> - | Clamp Cap Discharge Current     | V <sub>2</sub> = 5V                      | -1      | -0.55                       |                             | mA(min)           |

| V <sub>8L</sub>       | Video Output Low Voltage        | V <sub>2</sub> = 0V                      | 0.5     | 0.9                         |                             | V(max)            |

| V <sub>8H</sub>       | Video Output High Voltage       | V <sub>2</sub> = 5V                      | 8.5     | 8.0                         |                             | V(min)            |

| V <sub>OS</sub>       | Comparator Input Offset Voltage | V <sub>6</sub> -V <sub>9</sub>           | ±0.5    | ± 25                        |                             | mV(max)           |

## **AC Dynamic Tests** S9 Closed, $V_5 = 0V$ , $V_6 = 4V$

| Symbol         | Parameter                          | Conditions                              | Тур | Tested<br>Limit (Note 1) | Design<br>Limit (Note 2) | Units<br>(Limits) |

|----------------|------------------------------------|-----------------------------------------|-----|--------------------------|--------------------------|-------------------|

| Av max         | Video Amplifier Gain               | $V_4 = 12V$                             | 8   | 5.5                      |                          | V/V(min)          |

| ΔAv 5V         | Attenuation @ 5V                   | Ref: Av max, $V_4 = 5V$                 | -10 |                          |                          | dB                |

| ΔAv 2V         | Attenuation @ 2V                   | Ref: Av max, V <sub>4</sub> = 2V        | -45 |                          |                          | dB                |

| THD            | Video Amplifier Distortion         | $V_4 = 5V, V_O = 1 V_{p-p}$             | 0.3 |                          |                          | %                 |

| f (-3dB)       | Video Amplifier Bandwidth (Note 3) | $V_4 = 12V, V_O = 100 \text{ mV}_{rms}$ | 200 |                          | 170                      | MHz(min)          |

| t <sub>r</sub> | Output Rise Time (Note 3)          | $V_O = 4 V_{p-p}$                       | 2.5 |                          |                          | ns                |

| t <sub>f</sub> | Output Fall Time (Note 3)          | $V_O = 4 V_{p-p}$                       | 3   |                          |                          | ns                |

Note 1: These parameters are guaranteed and 100% production tested.

Note 2: Design limits are guaranteed (but not 100% production tested). These limits are not used to calculate outgoing quality levels.

Note 3: When measuring video amplifier bandwidth or pulse rise and fall times, a double sided full ground plane printed circuit board without socket is recommended.

**Note 4:** Operating Ratings indicate conditions of which the device is functional, but does not guarantee specific performance limits. For guaranteed specifications and test conditions, see Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

## FIGURE 2. LM1201 AC/DC Test Circuit

Note: When  $V_5 \le 0.8V$  and S9 is closed, DC feedback around the Video Amplifier is provided by the clamp comparator. Under these conditions sine wave or 50% duty cycle square waves can be used for test purposes. The low frequency dominant pole is determined by C2 at Pin 2. Capacitor C9 at pin 9 prevents overloading the clamp comparator inverting input. See applications section for additional information.

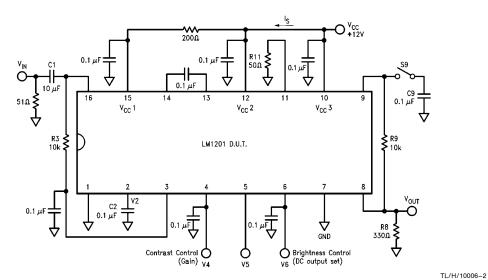

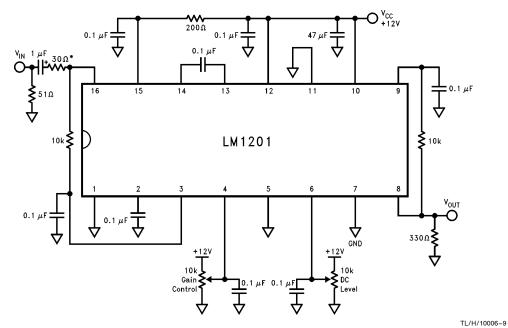

#### FIGURE 3. Typical Application of the LM1201

\*  $30\Omega$  resistor is added to the input pin for protection against current surges coming from the  $10~\mu\text{F}$  input capacitor. By increasing this resistor to well over  $100\Omega$  the rise and fall times of the LM1201 can be increased for EMI considerations.

#### APPLICATIONS INFORMATION

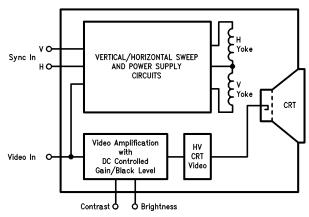

Figure 4 shows the block diagram of a typical analog monochrome monitor. The monitor is used with CAD/CAM work stations, PCs, arcade games and in a wide range of other applications that benefit from the use of high resolution display terminals. Monitor characteristics may differ in such ways as sweep rates, screen size, or in video amplifier speed but will still be generally configured as shown in Figure 4. Separate horizontal and vertical sync signals may be required or they may be contained as a composite signal in the video input signal. The video input signal is usually

supplied by coaxial cable which is terminated in  $75\Omega$  at the monitor input and internally AC coupled to the video amplifier. The input signal is approximately 1V peak-to-peak in amplitude and at the input of the high voltage video section, approximately 6V peak-to-peak. At the cathode of the CRT the video signals can be as high as 60V peak to peak. The block in *Figure 4* labeled "Video Amplification with DC Controlled Gain/Black Level" contains the function of the LM1201 video amplifier system.

TL/H/10006-4

FIGURE 4. Typical Monochrome Monitor Block Diagram

## **Circuit Description**

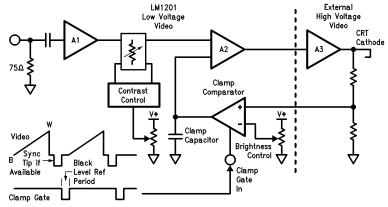

Figure 5 is a block diagram of the LM1201 along with the contrast and brightness controls. The contrast control is a DC operated attenuator which varies the AC gain of the amplifier without introducing any signal disortions or DC output shift. The brightness control function requires a "sample and hold" circuit (black level clamp) which holds the DC bias of the video amplifier and CRT cathodes constant during the black level reference portion of the video waveform. The clamp comparator, when gated on during this reference period, will charge or discharge the clamp capacitor until the non-inverting input of the clamp comparator matches that of the inverting input voltage which was set by the brightness control.

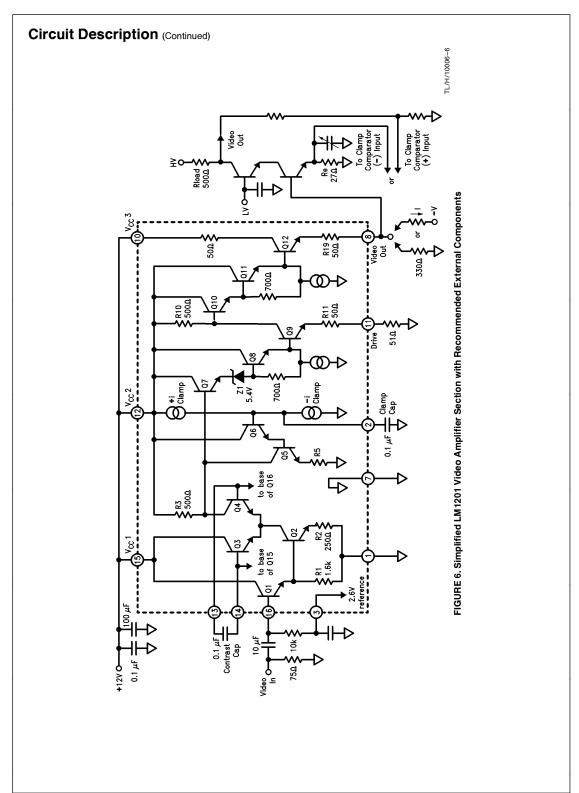

Figure 6 is a simplified schematic of the LM1201 video amplifier along with the recommended external components. The IC pin numbers are circled with all external components shown outside of the dashed line. The video input is applied

to pin 16 via the 10  $\mu\text{F}$  coupling capacitor. DC bias to the video input is through the 10  $k\Omega$  resistor which is connected to the 2.6V reference at pin 3. The low frequency roll-off of the amplifier is set by these two components. Transistor Q1 buffers the video signal to the base of Q2. The Q2 collector current is then directed to the V<sub>CC1</sub> supply through Q3 or to  $V_{CC2}$  through Q4 and the 500 $\Omega$  load resistor depending upon the differential DC voltage at the bases of Q3 and Q4. The Q3 and Q4 differential base voltage is determined by the contrast control circuit which is described below. The black level DC voltage at the collector of Q4 is maintained by Q5 and Q6 which are part of the black level clamp circuit also described below. The video signal appearing at the collector of Q4 is then buffered by Q7 and level shifted down by Z1 and Q8 to the base of Q9 which will then provide additional system gain.

FIGURE 5. Block Diagram of LM201 Video Amplifier with Contrast and Black Level Control

TL/H/10006-5

#### Circuit Description (Continued)

The "Drive" pin will allow the user to set the maximum gain of the amplifier based on the range of input video signal levels and the CRT stage gain if it is fixed or limited. When using three LM1201 devices for high resolution RGB applications, the "Drive" pin allows the user to trim the gain of each channel to correct for differences in the three CRT cathodes. A small capacitor (12 pF) in shunt with a  $51\Omega$ drive resistor at this pin will extend the high frequency gain of the video amplifier by compensating for some of the internal high frequency roll off. The  $51\Omega$  resistor will set the system gain to approximately 8 or 18 dB. The video signal at the collector of Q9 is buffered and level shifted down by Q10 and Q11 to the base of the output emitter follower Q12. Between the emitter of Q12 and the video output pin is a  $50\Omega$  resistor which is included to prevent spurious oscillations when driving capacitive loads. An external emitter resistor must be added between the video output pin and ground. The value of this resistor should not be less than 330 $\Omega$ , otherwise package power limitations may be exceeded when worst case (high supply, max supply current, max temp) calculations are made. If negative going pulse slewing is a problem because of high capacitive loads (>10 pF), a more efficient method of emitter pull down would be to connect a suitable resistor to a negative supply voltage. This has the effect of a current source pull down when the minus supply voltage is -12V, and the emitter current is approximately 10 mA. The system gain will also increase slightly because less signal will be lost across the internal  $50\Omega$  resistor. Precautions must be taken to prevent the video output pin from going below ground since IC substrate currents may cause erratic operation. The collector current from the video output transistor is returned to the power supply at  $V_{CC3}$ , pin 10. When making power dissipation calculations note that the datasheet specifies only the  $V_{CC1}$  and  $V_{CC2}$  supply currents at 12V. The IC power dissipation contribution of  $V_{CC3}$  is dependent upon the video output emitter pull down load.

In normal operation the minimum black level voltage that can be set at the video output pin is approximately 2V at maximum contrast setting. In applications that require a lower black level voltage, a resistor (approximately 16  $k\Omega$ ) can be added from pin 3 to ground. This has the effect of raising the DC voltage at the collector of Q4 which will extend the range of the black level clamp by allowing Q5 to remain active. In applications that require video amplifier shutdown due to fault conditions detected by monitor protection circuits, pin 3 and the wiper arms of the contrast and brightness controls can be grounded without harming the IC. This assumes some series resistance between the top of the control potentiometers and  $V_{\rm CC}$ .

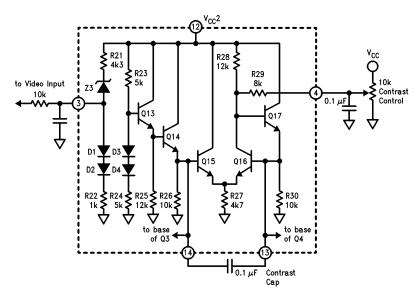

Figure 7 shows the internal construction of the pin 3 2.6V reference circuit which is used to provide temperature and supply voltage tracking compensation for the video amplifier input. The value of the external DC biasing resistors should not be larger than 10  $k\Omega$  when using more than one LM1201 (e.g. in RGB systems) because minor differences in input bias currents on the individual video amplifiers may cause offsets in gain.

FIGURE 7. LM1201 Video Input Voltage Reference and Contrast Control Circuits

TL/H/10006-7

## Circuit Description (Continued)

Figure 7 also shows how the contrast control circuit is configured. Resistors R23, R24, diodes D3, D4, and transistor Q13 are used to establish a low impedance zero TC half supply voltage reference at the base of Q14. The differential amplifier formed by Q15, Q16 and feedback transistor Q17 along with resistors R27, R28 establish a differential base voltage for Q3 and Q4 in Figure 6. When externally adding or subtracting current from the collector of Q16, a new differential voltage is generated that reflects the change in the ratio of currents in Q15 and Q16. To provide voltage control of the Q16 current, resistor R29 is added between the Q16 collector and pin 4. A capacitor should be added from pin 4 to ground to prevent noise from the contrast control pot from entering the IC.

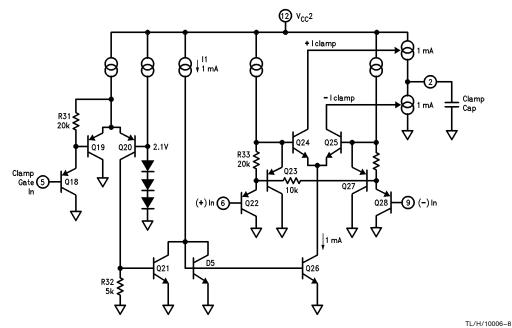

Figure 8 is a simplified schematic of the clamp gate and clamp comparator section of the LM1201. The clamp gate circuit consists of a PNP input buffer transistor (Q18), a PNP emitter coupled pair referenced on one side to 2.1V (Q19, Q20) and an output switch (Q21). When the clamp gate input at pin 5 is high (>1.5V), the Q21 switch is on and

shunts the I1 1mA current to ground. When pin 5 is low (<1.3V), the Q21 switch is off and the I1 1mA current source is mirrored or "turned around" by reference diode D5 and Q26 to provide a 1mA current source for the clamp comparator. The inputs to the comparator are similar to the clamp gate input except that an NPN emitter coupled pair is used to control the current which will charge or discharge the clamp capacitor at pin 2. PNP transistors are used at the inputs because they offer a number of advantages over NPNs. PNPs will operate with base voltages at or near ground and will usually have a greater reverse emitter-base breakdown voltage (BVebo). Because the differential input voltage to the clamp comparator during the video scan period could be greater than the BVebo of NPN transistors, resistor R34 with a value one half that of R33 or R35 is connected between the bases of Q23 and Q27. This resistor will limit the maximum differential input to Q24, Q25 to approximately 350 mV. The clamp comparator common mode range extends from ground to approximately 9V and the maximum differential input voltage is  $V_{\mbox{\footnotesize{CC}}}$  and ground.

FIGURE 8. Simplified Schematic of LM1201 Clamp Gate and Clamp Comparator Circuits

# **Applications Information**

Figure 9 shows the configuration of a high frequency amplifier with non-gated DC feedback. Pin 5 is tied low to turn on the clamp comparator (feedback amplifier). The inverting input (pin 9) is connected to the amplifier output from a low

pass filter. Additional low frequency filtering is provided by the clamp capacitor. The Drive pin is grounded to allow for the widest range of output signals. Maximum output swing is achieved when the DC output is set to approximately 4.5V.

FIGURE 9. High Frequency Amplifier/Attenuator Circuit with Non-Gated DC Feedback (Non-Video Applications)

## **Applications Information (Continued)**

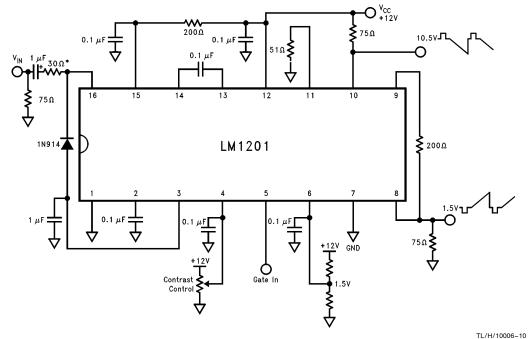

Figure 10 shows the LM1201 set up as a video amplifier with biphase outputs. Because the collector of output transistor Q12 is the only internal connection to  $V_{\rm CC3}$ , a  $75\Omega$  termination to the power supply voltage allows one to obtain inverted video at pin 10. Black level on the non-inverted video output (pin 8) is set to 1.5V by the voltage divider on pin 6.

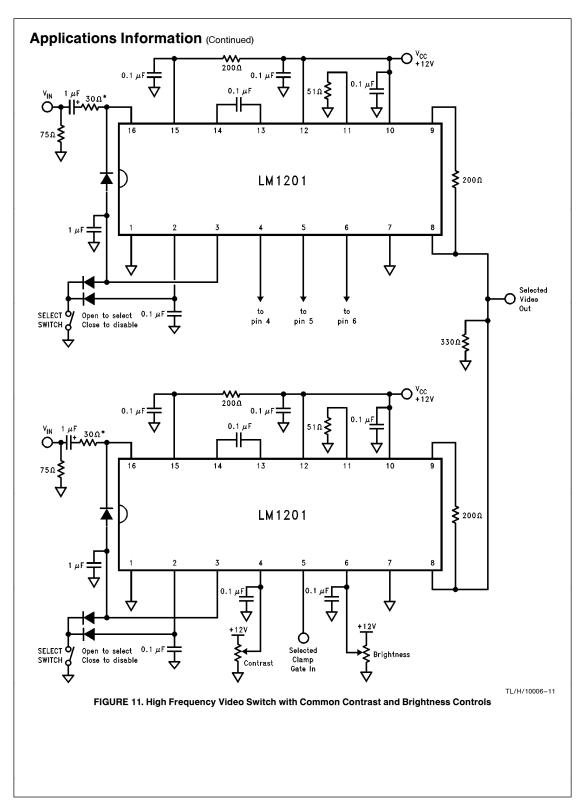

Figure 11 shows how a high frequency video switch may be designed using multiple LM1201 devices. All outputs can

be OR'ed together assuming no more than one channel is selected at any given time. Channel selection is accomplished by keeping the appropriate SELECT SWITCH open. Closing the SELECT SWITCH on a given channel disables that channel's output (pin 8) leaving it in a high impedance state. A single pair of contrast and brightness potentiometers control the selected channel's gain and output DC level

FIGURE 10. Preclamped Video Amplifier with Biphase Outputs

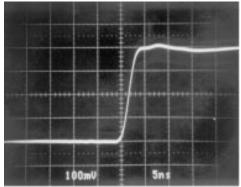

## Rise Time No Socket

TL/H/10006-12

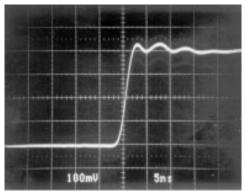

#### Rise Time In Socket

TL/H/10006-13

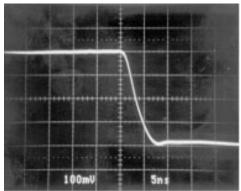

#### Fall Time No Socket

TL/H/10006-14

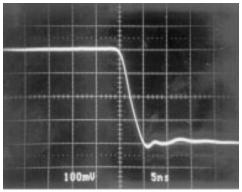

HP8082 pulse generator HP10241A 10:1 voltage divider HP1120A 500 MHz FET probe Tektronix 2465A 350 MHz scope

Scale for All Photos—Vert: 1V/Div Horiz: 5 ns/Div

#### **Fall Time In Socket**

TL/H/10006-15

- Actual output signal swings

4 V<sub>p-p</sub> (10:1 divider is used)

Contrast is set to maximum

V<sub>IN</sub> = 500 mV<sub>p-p</sub>

R<sub>DRIVE</sub> = 50Ω

Vertical scale is actually 1V/div and not 100 mV/div due to 10:1 attenuator used.

Outputs are centered at 4V DC.

TL/H/10006-16

**Note:** The p.c.b. layout shown above is suitable for evaluating the performance of the LM1201. Although it is similar to the typical application circuit of Figure 3, there is no c.r.t. driver stage. Instead, a feedback resistor is connected between Pins 8 and 9 and the brightness control is connected to Pin 6. Again, for best results, a socket should not be used for the LM1201.

#### COMPONENT VALUES:

| R1  | $75\Omega$ , 5%, 1/4 watt, carbon composition     | C1  | 0.1 $\mu$ F, ceramic          |

|-----|---------------------------------------------------|-----|-------------------------------|

| R3  | 10 k $\Omega$ , 5%, 1/4 watt, carbon composition  | C2  | 0.1 $\mu$ F, ceramic          |

| R4  | $50\Omega$ , 5%, 1/4 watt, carbon composition     | C4  | 0.1 $\mu$ F, ceramic          |

| R5  | $200\Omega$ , 5%, 1/4 watt, carbon composition    | C5  | 0.1 μF, ceramic               |

| R6  | 75 $\Omega$ , 5%, 1/4 watt, carbon composition    | C6  | 10 $\mu$ F/6V, electrolytic   |

| R7  | $330\Omega$ , 5%, 1/4 watt, carbon composition    | C7  | 0.1 $\mu$ F, ceramic          |

| R8  | 680 k $\Omega$ , 5%, 1/4 watt, carbon composition | C8  | 0.1 $\mu$ F, ceramic          |

| R9  | 10 k $\Omega$ , trim pot, helitrim model 91       | C9  | 0.1 $\mu$ F, ceramic          |

| R10 | 5.1 k $\Omega$ , 5%, 1/4 watt, carbon composition | C10 | 0.1 $\mu$ F, ceramic          |

| R11 | 43 k $\Omega$ , 5%, 1/4 watt, carbon composition  | C11 | 0.1 $\mu$ F, ceramic          |

| R12 | 12 k $\Omega$ , 5%, 1/4 watt, carbon composition  | C12 | 0.1 $\mu$ F, ceramic          |

| R13 | 10 k $\Omega$ , trim pot, helitrim model 91       | C13 | 100 $\mu$ F/15V, electrolytic |

| R14 | 2 k $\Omega$ , 5%, 1/4 watt, carbon composition   | C14 | 0.001 $\mu$ F, mica           |

| R15 | $200\Omega$ , 5%, 1/4 watt, carbon composition    | C15 | 0.1 $\mu$ F, ceramic          |

| IC1 | LM1201                                            |     |                               |

| IC2 | LM1881                                            |     |                               |

|     |                                                   |     |                               |

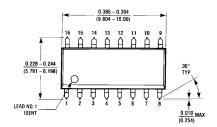

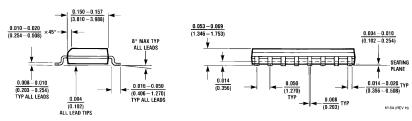

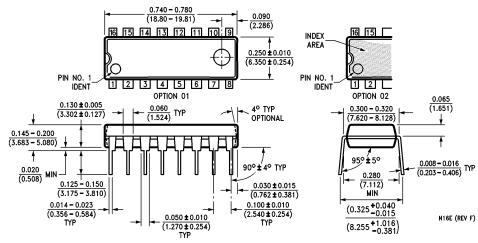

# Physical Dimensions inches (millimeters) unless otherwise noted

16-Lead (0.1500" Wide) Small Outline Molded Package (M) Order Number LM1201M NS Package Number M16A

16-Lead Molded Dual-In-Line Package (N) Order Number LM1201N NS Package Number N16E

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor** National Semiconducto Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

http://www.national.com

**National Semiconductor**

Europe Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 180-530 85 85 English Tel: +49 (0) 180-532 78 32 Français Tel: +49 (0) 180-532 93 86 Italiano Tel: +49 (0) 180-534 16 80 Europe

Hong Kong Ltd.

13th Floor, Straight Block,

Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

**National Semiconductor**

National Semiconductor Japan Ltd.

Tel: 81-043-299-2308

Fax: 81-043-299-2408